智能變電站動態重構技術研究

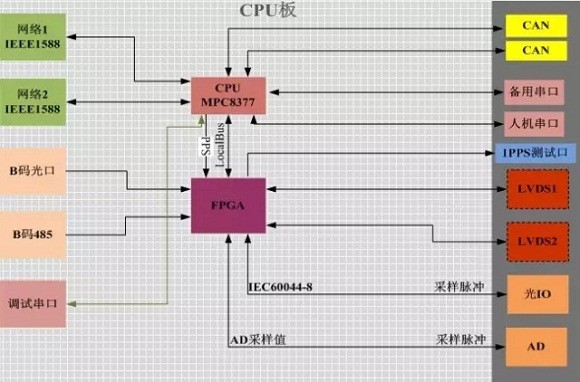

2.2.1CPU板

CPU板包括CPU主板和CPU的FPGA板

1)CPU板主板

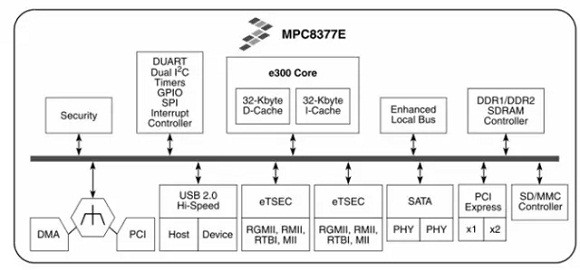

CPU插件的主CPU采用MPC8377E。MPC8377E處理器采用e300core,主頻可達667MHz;帶MMU,DDR2內存最高400MHz;32位LocalBus,最高133MHz,支持NandFlash啟動;32位PCI總線,最高66MHz;2個PCI-E接口;2個SATA接口;2個10/100/1000Mbit的以太網接口;1個USB2.0接口;2個UART;2個I2C;1個SPI。如圖4所示。

圖4CPU板插件硬件框架

CPU板主變的主要資源如圖5所示。

圖5MPC8377模塊框圖

2)CPU板的FPGA板

CPU板的FPGA實現的功能比較復雜,為數據處理的核心部分。

FPGA同時接收左向和右向網絡板FPGA的數據,并按照相應的順序填寫到SDRAM中,并使能中斷信號,提示CPU可以接收網絡數據。

由于SDRAM不能同時讀寫。當CPU響應FPGA中斷接收數據時,將會同時占用FPGA和一片SDRAM的LocalBus,如果此時網絡板FPGA有數據包傳遞進來的話,就只能緩沖到第二塊SDRAM。然后發起中斷,提示數據到來,CPU將會讀取第二塊SDRAM,以此類推,由兩塊SDRAM實現了雙口RAM的功能。

由于CPU與FPGA之間只有一個LocalBus接口,當CPU與SDRAM進行數據通信時,LocalBus會被占用,此時CPU無法訪問FPGA,最好增加一個SPI接口,CPU可以通過SPI接口適時訪問FPGA。

2.2.2網絡接口板

每個網絡接口板配置8個網絡接口。每個以太網口均有link及act指示燈,用于表征各網絡接口及接口板的工作狀態。通過更換元器件可實現網絡的電接口或光接口。網絡接口板通過FPGA實現以太網口驅動、網絡接口板與CPU板的通信。網絡接口板與背板聯絡,為光纖接口和CPU通信傳遞信息。網絡接口板與CPU板之間采用光纖通信。

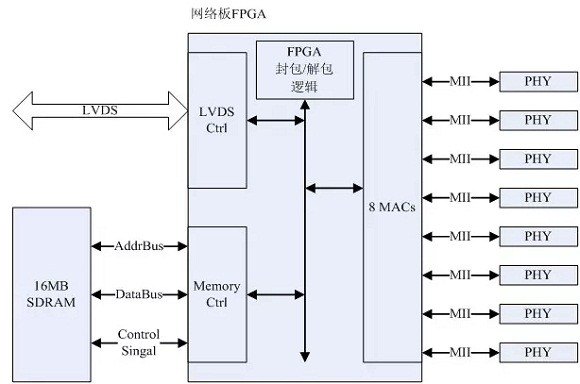

網絡接口網絡板硬件框圖如圖6所示,主要由以下三部分組成:(1)FPGA模塊,主要實現FPGA封包解包邏輯、8個10/100MMACs、LVDS高速總線控制器以及SDRAM存儲器控制器。(2)SDRAM模塊,主要實現網絡數據幀的存儲、轉發。(3)PHYs模塊,包括8個10/100M以太網PHY芯片。PHY芯片建議選RTL8208B,該芯片為8路10/100Base-T/TX和100Base-FXPHY,也可以選擇RTC8201或IP101A等芯片。板采用子母板設計方式。

圖6網絡板FPGA功能模塊

2.3FPGA功能設計

2.3.1系統邏輯

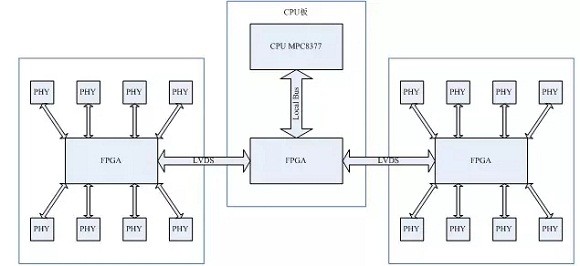

FPGA設計包括CPU板FPGA設計和網絡板FPGA設計兩部分。網絡板的FPGA主要實現擴展網絡功能和網絡數據的解碼功能;CPU板的FPGA主要實現CPU與FPGA之間的數據通信以及與網絡板FPGA的交互數據的功能。功能如圖7所示。

圖7FPGA系統連接圖

2.3.2FPGA邏輯功能

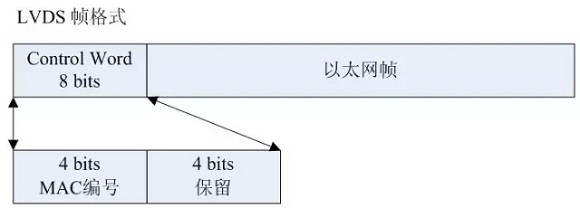

其主要功能是完成8個以太網MAC與串行的高速LVDS總線之間的通信。可以實現8個10/100MMAC與8個PHY芯片進行數據交互。為每一個MAC設計兩個幀的緩沖區,每個緩沖區大小為2048字節;同時可以實現LVDS本方案考慮使用LVDS接口實現FPGA之間的互聯。FPGA收到網絡數據包之后,通過8b/10b編碼轉換成(至少)1Gbps的網絡數據流,將其傳輸到CPU板的FPGA。

但由于封包解包邏輯8個以太網MAC的數據是并行的,而LVDS總線是串行的,所以還要考慮:LVDS選擇性的從8個MAC讀取數據傳輸。其選擇MAC的順序是1至8,而后繞回到1;其選擇依據是當前MAC的緩沖區是否有合法的數據幀,如果有則發送,沒有則直接跳過。LVDS傳輸的幀格式如圖8所示。

圖8LVDS幀格式

結論

本文根據智能變電站二次功能實現的工程設計,研究了智能變電站二次系統動態重構,提出了動態重構功能的硬件及軟件解決方案。在研究過程中,以智能變電站二次功能實現的各個環節為基礎,研究了智能變電站基于信息共享的二次設備功能軟件構造技術及功能軟件組件實現技術。

重構技術在智能變電站運行及維護工作中的自愈、自適應、自恢復等方面具有一定優勢,為智能變電站二次系統提供了新的手段,增加了二次系統運行的靈活性,有利于推動變電站智能化進程。

責任編輯:電朵云

-

權威發布 | 新能源汽車產業頂層設計落地:鼓勵“光儲充放”,有序推進氫燃料供給體系建設

2020-11-03新能源,汽車,產業,設計 -

中國自主研制的“人造太陽”重力支撐設備正式啟運

2020-09-14核聚變,ITER,核電 -

探索 | 既耗能又可供能的數據中心 打造融合型綜合能源系統

2020-06-16綜合能源服務,新能源消納,能源互聯網

-

新基建助推 數據中心建設將迎爆發期

2020-06-16數據中心,能源互聯網,電力新基建 -

泛在電力物聯網建設下看電網企業數據變現之路

2019-11-12泛在電力物聯網 -

泛在電力物聯網建設典型實踐案例

2019-10-15泛在電力物聯網案例

-

權威發布 | 新能源汽車產業頂層設計落地:鼓勵“光儲充放”,有序推進氫燃料供給體系建設

2020-11-03新能源,汽車,產業,設計 -

中國自主研制的“人造太陽”重力支撐設備正式啟運

2020-09-14核聚變,ITER,核電 -

能源革命和電改政策紅利將長期助力儲能行業發展

-

探索 | 既耗能又可供能的數據中心 打造融合型綜合能源系統

2020-06-16綜合能源服務,新能源消納,能源互聯網 -

5G新基建助力智能電網發展

2020-06-125G,智能電網,配電網 -

從智能電網到智能城市